Synopsys Design Compiler

Synopsys Design Compiler Tutorial

MOUNTAIN VIEW, Calif., Feb. 8, 2018 // - Synopsys, Inc. (Nasdaq: SNPS) completed its acquisition of PhoeniX B.V., headquartered in Enschede, the Netherlands, a global supplier of photonic chip design solutions. With the acquisition, Synopsys is the leading provider of photonic integrated circuit design automation solutions for a wide range of application requirements ranging from data communications to sensors and biomedical devices. The terms of the deal, which is not material to Synopsys financials, are not being disclosed. Photonics, or the manipulation and movement of light waves, represents a growing opportunity and challenge in integrated circuit design. As data rate needs increase, there is growing requirement to reduce power consumption in data transmission.

Thus, the use of photonic switching and transmission are becoming a more integral part of high-speed electronic designs. The acquisition enables Synopsys to enhance and broaden the current photonics design automation offering by adding photonic aware physical layout capabilities, enabled by support for foundry-specific process design kits (PDK).

Additionally, the acquired technologies will extend Synopsys' Custom Compiler™ solution for photonic applications. With this acquisition IC design teams will have access to widely used, high-quality IC and photonic design solutions from a single provider with a single support channel. 'The PhoeniX Software technology will bolster our photonics solution in both optical and custom design,' said Dr. Howard Ko, general manager of Synopsys' Silicon Engineering Group 'the PhoeniX Software physical layout tools are a natural complement to our existing photonics solutions portfolio. The acquisition underscores our commitment to our photonics portfolio to help designers meet their evolving photonic integrated circuit design requirements.' About Synopsys Synopsys, Inc. (Nasdaq: SNPS) is the Silicon to Software™ partner for innovative companies developing the electronic products and software applications we rely on every day.

As the world's 15 th largest software company, Synopsys has a long history of being a global leader in electronic design automation (EDA) and semiconductor IP and is also growing its leadership in software security and quality solutions. Whether you're a system-on-chip (SoC) designer creating advanced semiconductors, or a software developer writing applications that require the highest security and quality, Synopsys has the solutions needed to deliver innovative, high-quality, secure products. Editorial Contacts: Simone Souza Synopsys, Inc.

650-584-6454 Investor Contact: Lisa Ewbank Synopsys, Inc. 650-584-1901 SOURCE Synopsys, Inc.

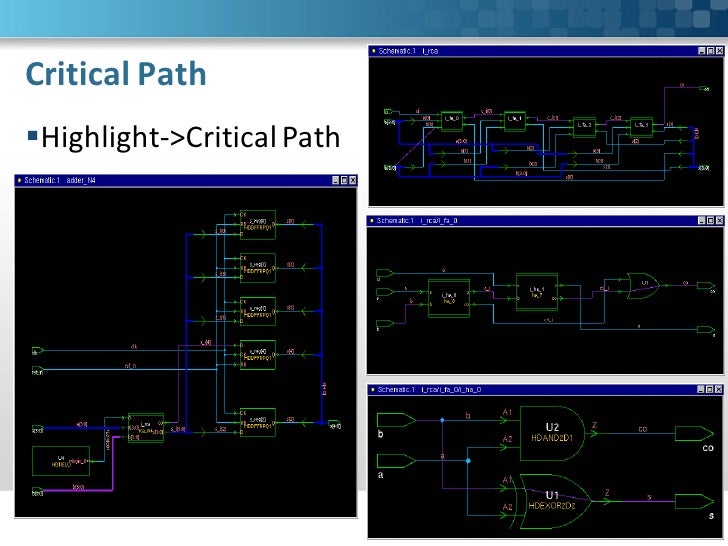

DC Ultra™ RTL synthesis solution enables users to meet today's design challenges with concurrent optimization of timing, area, power and test. DC Ultra includes innovative topographical technology that enables a predictable flow resulting in faster time to results. Topographical technology provides timing and area prediction within 10% of the results seen post-layout enabling designers to reduce costly iterations between synthesis and physical implementation. DC Ultra also includes a scalable infrastructure that delivers 2X faster runtime on quad-core platforms. DC Ultra is the core of Synopsys' comprehensive RTL synthesis solution, including Power Compiler™, DesignWare®, PrimeTime®, and DFTMAX™. Design Compiler Graphical is available as an add-on to DC Ultra that includes best-in-class quality-of-results, congestion prediction and alleviation capabilities, physical viewer, and floorplan exploration.

- How can the answer be improved?

- Feb 07, 2018 Synopsys, Inc. A global supplier of photonic chip design. The acquired technologies will extend Synopsys' Custom Compiler™ solution for.

Send comments on the documentation by going to then clicking “Enter a Call to the Support Center.” Design Compiler®.

Additionally Design Compiler Graphical produces physical guidance to IC Compiler, place-and-route solution for tighter correlation to layout and faster placement runtime.